**Precedence** from highest to lowest: Not (') And (·) Or (+) minterm - product term - SOP - find 1 maxterm - sum term - POS - find 0

Each minterm is the complement of the maxterm

SOP - 2-level AND-OR/NAND circuit POS - 2-level OR-AND/NOR circuit

PLAs may not be able to implement a given mapping due Multivibrator: a class of sequential circuits to not having enough minterms.

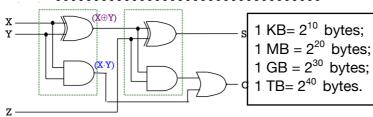

Half Adder:

$X+X\cdot Y=X$

Active-High

10100 R

10001 S

1

S R

0 0

1 O

1

$X+X'\cdot Y=X+Y$

$C = X \cdot Y$ ,  $S = X' \cdot Y + X \cdot Y' = X \oplus Y$

K-Maps -> SOP

Gate-Level (SSI) Design: Full-Adder, Code Converter

$C = X \cdot Y + (X \oplus Y) \cdot Z, S = X \oplus (Y \oplus Z)$

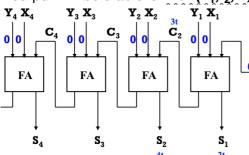

Block-Level Design: block: 4-bit parallel/ripple-carry adder:  $C_{i+1} = X_i \cdot Y_i + (X_i \oplus Y_i) \cdot C_i$ ,  $S_i = X_i \oplus Y_i \oplus C_i$

$X \cdot Y + X \cdot Z + Y \cdot Z = X \cdot Y + X' \cdot Z$  $Y' \cdot Z' + Y \cdot Z = (Y \oplus Z)'$

$Y' \cdot Z + Y \cdot Z' = Y \oplus Z$  $X+Y=(X\oplus Y)+X\cdot Y$

Given a logic gate with delay t. If inputs are stable at times t<sub>1</sub>, t<sub>2</sub>, ..., t<sub>n</sub>, then the earliest time in which the

Q' 00110

No change

Reset

Set

output will be stable is:  $max(t_1,t_2,...,t_n) + t$

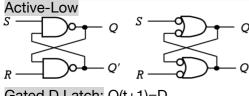

S-R Latch:  $Q(t+1)=S+R'\cdot Q$ ,  $S\cdot R=0$

Q(t+1)

Q(t)

0

1

indeterminate

T flip-flop: Single input version of the **5**-K flip-flop Q(t+1)=T•Q'+T'•Q

| T | CLK      | Q(t+1) | Comments  |

|---|----------|--------|-----------|

| 0 | <b>↑</b> | Q(t)   | No change |

| 1 | <b>↑</b> | Q(t)'  | Toggle    |

Flip-Flops: synchronous bistable

- Output changes state at a specified point on a triggering input called the clock.

- Change state either at the positive (rising) edge, or at the negative (falling) edge of the clock signal. Note ">" symbol at the clock input.

> positive, o> negative edge-triggered

Positive pulses Negative edges Positive edges

S

·C

| Jaleu | D Late | ch: Q(t+1)=D |

|-------|--------|--------------|

| EN    | D      | Q(t+1)       |

|       |        |              |

| EN | D | Q(t+1) |           |

|----|---|--------|-----------|

| 1  | 0 | 0      | Reset     |

| 1  | 1 | 1      | Set       |

| 0  | X | Q(t)   | No change |

A positive edge-triggered D flip-flop formed with an S-R flip-flop.

CLK

combinational circuit: each output depends entirely on the immediate (present) inputs

sequential circuit: each output depends on both present inputs and state

- Synchronous: outputs change only at specific time

- Asynchronous: outputs change at any time

- § Bistable (2 stable states)

- Latches and flip-flops.

- differ in the methods used for changing state.

- § Monostable or one-shot (1 stable state)

- S Astable (no stable state)

Memory element: a device which can remember value indefinitely, or change value on command from its inputs.

Two types of triggering/activation

- Level/Pulse-triggered

- § Latches

- § ON = 1, OFF = 0

- Edge-triggered

- § Flip-flops

input/output = x/y

0/1

0/1

1/0

0/1

- Secondary Positive edge-triggered (ON = 0 to 1; OFF = other time)

- Negative edge-triggered (ON = 1 to 0: OFF = other time)

|   | Present | it Next Stat             |                               | Ou  | itput       |  |

|---|---------|--------------------------|-------------------------------|-----|-------------|--|

|   | State   | x=0                      | <i>x</i> =1                   | x=0 | <i>x</i> =1 |  |

| 0 | AB      | $A^{\dagger}B^{\dagger}$ | A <sup>+</sup> B <sup>+</sup> | У   | У           |  |

|   | 00      | 00                       | 01                            | 0   | 0           |  |

|   | 01      | 00                       | 11                            | 1   | 0           |  |

|   | 10      | 00                       | 10                            | 1   | 0           |  |

|   | 11      | 00                       | 10                            | 1   | 0           |  |

S-R flip-flop: On the triggering edge of the clock pulse positive edge-triggered S-R flip-flop

| S | R | CLK        | Q(t+1) | Comments  |

|---|---|------------|--------|-----------|

| 0 | 0 | Х          | Q(t)   | No change |

| 0 | 1 | $\uparrow$ | 0      | Reset     |

| 1 | 0 | <b>↑</b>   | 1      | Set       |

| 1 | 1 | $\uparrow$ | ?      | Invalid   |

X = irrelevant ("don't care")

$\uparrow$  = clock transition LOW to HIGH

D flip-flop: On the triggering edge of the clock pulse

| D | CLK        | Q(t+1) | Comments |

|---|------------|--------|----------|

| 1 | <b>↑</b>   | 1      | Set      |

| 0 | $\uparrow$ | 0      | Reset    |

# $\uparrow$ = clock transition LOW to HIGH

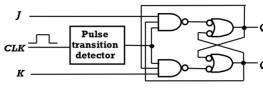

J-K flip-flop: Q and Q' are fed back to the pulse-steering NAND gates.

| J | Κ | CLK      | Q(t+1) | Comments  |

|---|---|----------|--------|-----------|

| 0 | 0 | <b>↑</b> | Q(t)   | No change |

| 0 | 1 | <b>↑</b> | 0      | Reset     |

| 1 | 0 | <b>↑</b> | 1      | Set       |

| 1 | 1 | <b>↑</b> | Q(t)'  | Toggle    |

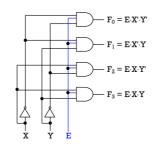

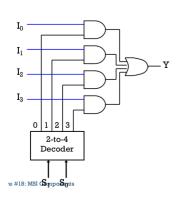

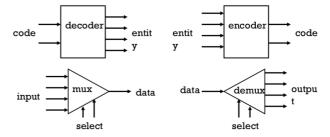

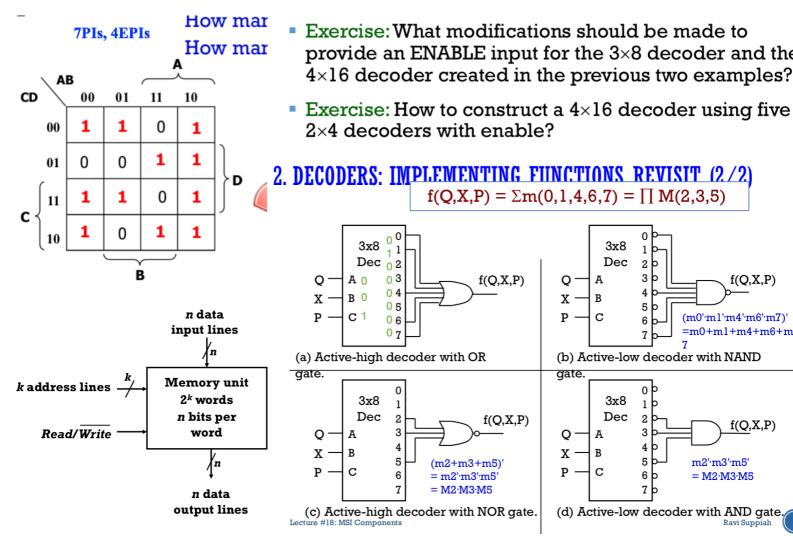

decoder: Convert binary information from n input lines to (a maximum of) 2<sup>n</sup> output lines.

- Known as n-to-m-line decoder, or simply n:m or n x m decoder (m  $\leq$  2n).

- May be used to generate 2<sup>n</sup> minterms of n input variables.

SOP = decoder to generate minterms + OR gate to form thesum

enable control signal: the device is only activated when the enable E = 1 (one-enable) (MSI is mainly 0-enable)

| X | Y | $\mathbf{F_0}$ | $\mathbf{F_1}$ | $\mathbf{F_2}$   | $\mathbf{F_3}$ |

|---|---|----------------|----------------|------------------|----------------|

| 0 | 0 | 1              | 0              | 0                | 0              |

| 0 | 1 | 0              | 1              | 0                | 0              |

| 1 | 0 | 0              | 0              | 1                | 0              |

| 1 | 1 | 0              | 0              | 0<br>0<br>1<br>0 | 1              |

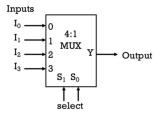

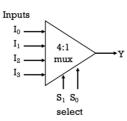

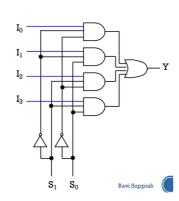

multiplexer: It steers one of 2<sup>n</sup> inputs to a single output line, using *n* selection lines. Also known as a *data selector*. priority encoder:

- · A number of input lines

- · A number of selection lines

- One output line

- Output of multiplexer is "sum of the (product of data lines and selection lines)"

- Example: Output of a 4-to-1 multiplexer is: Y =  $I_0 \cdot (S_1 \cdot S_0) + I_1 \cdot (S_1 \cdot S_0) + I_2 \cdot (S_1 \cdot S_0) +$

$$I_{3} \cdot (S_{1} \cdot S_{0}) = I_{0} \cdot m_{0} + I_{1} \cdot m_{1} + I_{2} \cdot m_{2} + I_{3} \cdot m_{3}$$

| $I_0$ | I <sub>1</sub> | I <sub>2</sub> | I <sub>3</sub> | $S_1$ | $S_0$ | Y  |

|-------|----------------|----------------|----------------|-------|-------|----|

| $d_0$ | $d_1$          | $d_2$          | $d_3$          | 0     | 0     | d  |

| $d_0$ | $d_1$          | $d_2$          | $d_3$          | 0     | 1     | d  |

| $d_0$ | $d_1$          | $d_2$          | $d_3$          | 1     | 0     | d- |

$d_0 \ d_1 \ d_2 \ d_3 \ 1 \ 1 \ d_3$

| $S_1$ | $S_0$ | Y              |

|-------|-------|----------------|

| 0     | 0     | $I_0$          |

| 0     | 1     | $\mathbf{I}_1$ |

| 1     | 0     | $I_2$          |

| 1     | 1     | $I_3$          |

A 2<sup>n</sup>-to-1-line multiplexer, or simply 2<sup>n</sup>:1 MUX, is made from an  $n:2^n$  decoder by adding to it  $2^n$  input lines, one to each AND gate.

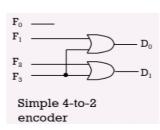

encoder: exactly one input line is high and the rest are low,

$$D_0 = F_1 + F_3$$

,  $D_1 = F_2 + F_3$

|                |                | _              |                |                |                |

|----------------|----------------|----------------|----------------|----------------|----------------|

| F <sub>0</sub> | $\mathbf{F_1}$ | $\mathbf{F_2}$ | $\mathbf{F_3}$ | $\mathbf{D_1}$ | $\mathbf{D_0}$ |

| 1              | 0              | 0              | 0              | 0              | 0              |

| 0              | 1              | 0              | 0              | 0              | 1              |

| 0              | 0              | 1              | 0              | 1              | 0              |

| 0              | 0              | 0              | 1              | 1              | 1              |

| 0              | 0              | 0              | 0              | X              | X              |

| 0              | 0              | 1              | 1              | X              | X              |

| 0              | 1              | 0              | 1              | X              | X              |

| 0              | 1              | 1              | 0              | X              | X              |

| 0              | 1              | 1              | 1              | X              | X              |

| 1              | 0              | 0              | 1              | X              | X              |

| 1              | 0              | 1              | 0              | X              | X              |

| 1              | 0              | 1              | 1              | X              | X              |

| 1              | 1              | 0              | 0              | X              | X              |

| 1              | 1              | 0              | 1              | X              | X              |

| 1              | 1              | 1              | 0              | X              | X              |

| 1              | 1              | 1              | 1              | X              | X              |

|                |                |                |                |                |                |

- · If two or more inputs or equal to 1, the input with the highest priority takes precedence.

- · If all inputs are 0, this input combination is considered invalid.

|                | Inp            | uts            | Outputs        |   |   |          |

|----------------|----------------|----------------|----------------|---|---|----------|

| $\mathbf{D}_0$ | $\mathbf{D}_1$ | $\mathbf{D}_2$ | $\mathbf{D}_3$ | f | g | <b>V</b> |

| 0              | 0              | 0              | 0              | X | X | 0        |

| 1              | 0              | 0              | 0              | 0 | 0 | 1        |

| X              | 1              | 0              | 0              | 0 | 1 | 1        |

| X              | X              | 1              | 0              | 1 | 0 | 1        |

| X              | X              | X              | 1              | 1 | 1 | 1        |

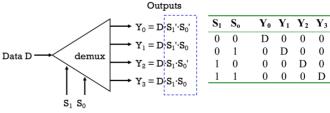

demultiplexers: Given an input line and a set of selection lines, a demultiplexer directs data from the input to one selected output line.

demultiplexer circuit is actually identical to a decoder with enable.

|          | $S_1 S_0$    |                |   |   |   |   |              |   |   |            |   |  |

|----------|--------------|----------------|---|---|---|---|--------------|---|---|------------|---|--|

| 1 -      | select       |                |   |   |   |   |              |   |   |            |   |  |

| , -<br>- | Q            | Q⁺             | 7 |   | Κ | _ | Q            | Q | • | S          | R |  |

|          | 0            | 0              | 0 |   | X |   | 0            | 0 |   | 0          | X |  |

|          | 0            | 1              | 1 |   | X |   | 0            | 1 |   | 1          | 0 |  |

|          | 1            | 0              | Х | ( | 1 |   | 1            | 0 |   | 0          | 1 |  |

|          | 1            | 1              | X | ( | 0 |   | 1            | 1 |   | X          | 0 |  |

|          | JK Flip-flop |                |   |   |   |   | SR Flip-flop |   |   |            |   |  |

|          | Q            | Q <sup>†</sup> |   | D |   |   |              | Q | G | <b>)</b> † | T |  |

|          | 0            | 0              |   | 0 |   |   |              | 0 |   | 0          | 0 |  |

|          | 0            | 1              |   | 1 |   |   |              | 0 | • | 1          | 1 |  |

|          | 1            | 0              |   | 0 |   |   |              | 1 | ( | 0          | 1 |  |

|          | 1            | 1              |   | 1 |   |   |              | 1 | • | 1          | 0 |  |

|          | D Flip-flop  |                |   |   |   |   | TFlip-flop   |   |   |            |   |  |

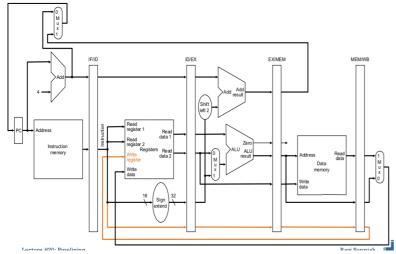

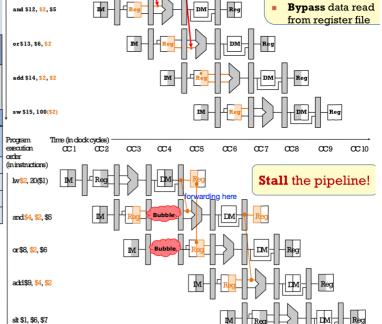

- § IF: Instruction Fetch

- § ID: Instruction Decode and Register Read

- § EX: Execute an operation or calculate an address

- § MEM: Access an operand in data memory

- § WB: Write back the result into a register

- At the end of a cycle, IF/ID receives (stores):

- Instruction read from InstructionMemory[ PC ]

- PC + 4

- PC + 4

beq

Also connected to one of the MUX's inputs (another coming later

| - 1    | uso con             | necteat                | o one c   | or the iv                                     | IUASI                                              | ipuis (a           | another | comm     | g later) |  |

|--------|---------------------|------------------------|-----------|-----------------------------------------------|----------------------------------------------------|--------------------|---------|----------|----------|--|

| I      | It the beg          | ginning o<br>egister s |           | At the end of a cycle ID/EX receives:         |                                                    |                    |         |          |          |  |

| *      | Register            | numbe                  | rs for re | eading                                        | ❖ Data values read from                            |                    |         |          |          |  |

|        | two regi            | sters                  |           |                                               | register file                                      |                    |         |          |          |  |

| *      | 16-bit of           | fset to b              | e sign-   |                                               | *                                                  | 32-bit             | immedi  | iate val | lue      |  |

|        | extende             | d to 32-1              | bit       |                                               | ❖ PC + 4                                           |                    |         |          |          |  |

|        | the beg             | -                      | 9         | At the end of a cycle EX/MEM receives:        |                                                    |                    |         |          |          |  |

| *      | Data val            | ues reac               |           | ❖ (PC + 4) + (Immediate x 4)                  |                                                    |                    |         |          |          |  |

| :      | register            | file                   |           |                                               | <ul> <li>ALU result</li> </ul>                     |                    |         |          |          |  |

| *      | 32-bit in           | nmediat                | e value   |                                               | isZero? signal                                     |                    |         |          |          |  |

| *      | PC + 4              |                        |           |                                               | <ul> <li>Data Read 2 from register file</li> </ul> |                    |         |          |          |  |

| At     | the beg             | inning o               | f a cycle | е                                             | At the end of a cycle                              |                    |         |          |          |  |

| E      | X/MEM re            | gister sı              |           | MEM/WB receives:                              |                                                    |                    |         |          |          |  |

| *      | (PC + 4)            | + (Imme                | ł)        | <ul> <li>ALU result</li> </ul>                |                                                    |                    |         |          |          |  |

| *      | ALU resu            | lt                     |           | Memory read data                              |                                                    |                    |         |          |          |  |

| *      | isZero?             | signal                 |           |                                               |                                                    |                    |         |          |          |  |

|        | Data Rea            |                        |           |                                               |                                                    |                    |         |          |          |  |

|        | the beg<br>EM/WB re |                        |           |                                               | At the end of a cycle                              |                    |         |          |          |  |

| *      | ALU resu            | lt                     |           | <ul> <li>Result is written back to</li> </ul> |                                                    |                    |         |          |          |  |

| *      | Memory              | read data              | a         |                                               | register file (if applicable)                      |                    |         |          |          |  |

|        |                     |                        |           |                                               | * There is a bug here                              |                    |         |          |          |  |

|        | EX Stage            |                        |           |                                               |                                                    | MEM Stage WB Stage |         |          |          |  |

|        | RegDst              | ALUSrc                 | ALU       | op                                            | Mem                                                | Mem                | Branch  | MemTo    | Reg      |  |

|        |                     |                        | op1       | op0                                           | Read                                               | Write              |         | Reg      | Write    |  |

| R-type | 1                   | 0                      | 1         | 0                                             | 0                                                  | 0                  | 0       | 0        | 1        |  |

| lw     | 0                   | 1                      | 0         | 0                                             | 1                                                  | 0                  | 0       | 1        | 1        |  |

| sw     | Х                   | 1                      | 0         | 0                                             | 0                                                  | 1                  | 0       | Х        | 0        |  |

|        |                     |                        |           |                                               |                                                    |                    |         |          |          |  |

0

Χ

O

Single Cycle

- § Cycle time:

- § CTseq =  $\sum_{k=1}^{N} T_k$

- § Tk = Time for operation in stage k

- § N = Number of stages

- § Total Execution Time for I instructions:

## Multi Cycle

- § Cycle time:

- § CTmulti =  $max(T_k)$

- § max(Tk) = longest stage duration among the N stages

- § Total Execution Time for I instructions:

- § Time<sub>multi</sub> = Cycles × CycleTime = I×Average

## **CPI**×CTmulti

§ Average CPI is needed because each instruction takes different number of cycles to finish

#### Pipeline Cycle

- § Cycle time:

- § CTpipeline =  $max(T_k) + T_d$

- § max(Tk) = longest time among the N stages

- § T<sub>d</sub> = Overhead for pipelining, e.g. pipeline register

- § Cycles needed for I instructions:

- § I + N -1

- § N 1 is the cycles wasted in filling up the pipeline

- § Total Execution Time for I instructions:

- § Timepipeline = Cycle × CTpipeline =  $(I + N 1) \times (max(T_k) + I)$

#### Ideal Speedup

- · Every stage takes the same amount of time

- No pipeline overhead T<sub>d</sub>=0

- Number of instructions I is much larger than number of stages N

Speedup<sub>pipeline</sub> = Time<sub>seq</sub> / Time<sub>pipeline</sub>

Pipeline processor can gain  ${\bf N}$  times speedup, where  ${\bf N}$  is the number of pipeline stages

Forward results from one stage to

another

### Write operation:

- Transfers the address of the desired word to the address lines.

- Transfers the data bits (the word) to be stored in memory to the data input lines.

- Activates the Write control line (set Read/Write to 0).

## Read operation:

- Transfers the address of the desired word to the address lines.

- Activates the Read control line (set Read/Write to 1).

| <b>Memory Enable</b> | Read/Write | Memory Operation        |

|----------------------|------------|-------------------------|

| 0                    | X          | None                    |

| 1                    | 0          | Write to selected word  |

| 1                    | 1          | Read from selected word |

- Two types of RAM

- Static RAMs use flip-flops as the memory cells.

- Dynamic RAMs use capacitor charges to represent data. Though simpler in circuitry, they have to be constantly refreshed.